# LaurTec

# AD9833 - Libreria ed applicazioni

Generatore di funzione DDS

Autore: Dario Di Turi

**ID:** UP0003-IT

#### **INFORMATIVA**

Come prescritto dall'art. 1, comma 1, della legge 21 maggio 2004 n.128, l'autore avvisa di aver assolto, per la seguente opera dell'ingegno, a tutti gli obblighi della legge 22 Aprile del 1941 n. 633, sulla tutela del diritto d'autore.

Tutti i diritti di questa opera sono riservati. Ogni riproduzione ed ogni altra forma di diffusione al pubblico dell'opera, o parte di essa, rappresenta una violazione della legge che tutela il diritto d'autore, in particolare non ne è consentito un utilizzo per trarne profitto.

La mancata osservanza della legge 22 Aprile del 1941 n. 633 è perseguibile con la reclusione o sanzione pecuniaria, come descritto al Titolo III, Capo III, Sezione II.

A norma dell'art. 70 è comunque consentito, per scopi di critica o discussione, il riassunto e la citazione, accompagnati dalla menzione del titolo dell'opera e dal nome dell'autore.

#### **AVVERTENZE**

I progetti presentati non hanno la certificazione CE, quindi non possono essere utilizzati per scopi commerciali nella Comunità Economica Europea.

Chiunque decida di far uso delle nozioni riportate nella seguente opera o decida di realizzare i circuiti proposti, è tenuto pertanto a prestare la massima attenzione in osservanza alle normative in vigore sulla sicurezza.

L'autore declina ogni responsabilità per eventuali danni causati a persone, animali o cose derivante dall'utilizzo diretto o indiretto del materiale, dei dispositivi o del software presentati nella seguente opera.

Si fa inoltre presente che quanto riportato viene fornito così com'è, a solo scopo didattico e formativo, senza garanzia alcuna della sua correttezza.

L'autore ringrazia anticipatamente per la segnalazione di ogni errore.

Tutti i marchi citati in quest'opera sono dei rispettivi proprietari.

# Indice

| Introduzione                                  | 4  |

|-----------------------------------------------|----|

| Applicazioni                                  |    |

| La Tecnica DDS                                | 5  |

| L'integrato AD9833                            |    |

| I registri di controllo dell'integrato AD9833 |    |

| Libreria AD9833 per PIC18                     |    |

| Applicazione I: Generatore di funzioni        |    |

| Applicazione II: Figure di Lissajou           | 17 |

| Conclusioni                                   |    |

| Bibliografia                                  |    |

| History                                       |    |

#### **Introduzione**

L'integrato AD9833, prodotto dall'Analog Device, è in grado di generare una forma d'onda sinusoidale, triangolare o quadra con la tecnologia DDS. L'integrato, tra le varie applicazioni, è utilizzabile come generatore di funzione da 0 a 12.5MHz con una risoluzione di 0,1Hz. Nel seguente progetto si presenta una libreria per PIC18 che permette facilmente di gestire l'AD9833 per mezzo di poche funzioni. A fine articolo è presentato un esempio di generatore di funzioni realizzato per mezzo della scheda Freedom II e l'AD9833.

### **Applicazioni**

La libreria software presentata nel seguente progetto, in combinazione con l'integrato AD9833, può avere le seguenti applicazioni:

- Generatore di funzioni.

- Modulatore di segnale.

- Tester per linee di trasmissione.

#### La Tecnica DDS

Prima di iniziare, vediamo la teoria relativa alla tecnologia integrata all'interno dell'AD9833, ovvero la tecnica DDS. DDS è l'acronimo di Direct Digital Synthesis, ed è un metodo per produrre una forma d'onda analogica, normalmente sinusoidale, generando un segnale tempo variante digitale, il quale viene poi convertito in analogico mediante un DAC (Digital Analog Converter) sfruttando un riferimento a frequenza fissa fornito da un oscillatore esterno.

Tutte le operazioni di sintesi della forma d'onda sono svolte in ambito digitale e questo offre numerosi vantaggi come la possibilità di commutare rapidamente le frequenze di uscita, una risoluzione in frequenza fine e dipendente, come si vedrà in seguito, dalla frequenza dell'oscillatore.

Per capire il funzionamento di questa tecnologia ed in particolare come riprodurre un segnale sinusoidale, è necessario innanzi tutto ricordare che un segnale sinusoidale può essere espresso con la funzione matematica  $a=\sin(\omega t)$ , la quale è periodica, ovvero si ripete allo stesso modo dopo un intervallo di tempo. Questa funzione è però non lineare, infatti per esempio il seno della somma di due angoli non è, come si potrebbe erroneamente pensare, uguale alla somma dei seni dei due angoli. La funzione inversa del seno infatti è  $\omega t$  =arcsin(a), un'altra funzione non lineare.

L'idea che sta alla base della tecnologia DDS è quella di non considerare la funzione seno ma considerare l'angolo di rotazione che invece è un'espressione lineare.

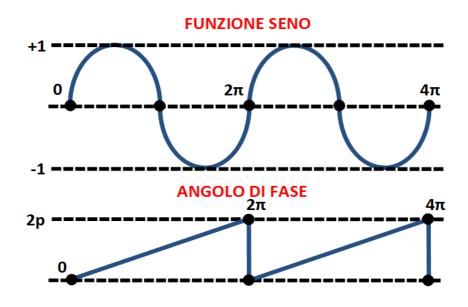

Considerando infatti quest'angolo in radianti, esso assume valori da 0 a  $2\pi$  e ad ogni angolo corrisponde un unico valore di ampiezza del segnale, così come mostrato in Figura 1.

**Figura 1:** Funzione seno e angolo di fase.

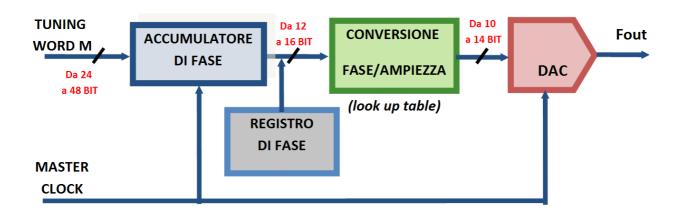

Lo schema a blocchi tipico di un dispositivo DDS è mostrato in Figura 2.

Figura 2: Schema a blocchi di un generatore a sintesi DDS.

Esso si compone da un accumulatore di fase, un blocco di conversione fase-ampiezza (una look up table), un DAC ed un registro di fase.

Dunque, per prima cosa, dovendo implementare questa logica in dominio digitale, è necessario dividere l'intervallo da 0 a  $2\pi$  in un numero di passi discreti e pari al numero di bit dell'accumulatore di fase, che è il primo blocco del sistema.

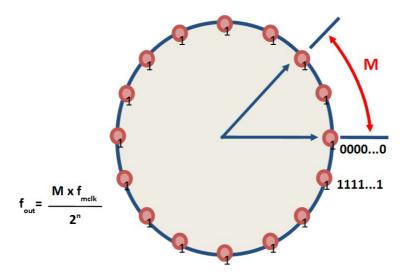

Possiamo rappresentare quest'intervallo su di una circonferenza, come riportato in Figura 3, nella quale è centrato un vettore rotante che si muove alla velocità angolare imposta dall'oscillatore esterno. Il vettore parte dal valore 0 fino all'ultimo valore consentito nell'accumulatore (dopo di che l'accumulatore va in overflow) e dunque riparte dall'inizio per tracciare un'altra sinusoide.

Figura 3: Schema a blocchi generatore a sintesi DDS

La frequenza del segnale sinusoidale in uscita può essere modificata impostando il passo M dell'accumulatore di fase (che in realtà non è altro che un contatore binario a modulo M), ovvero l'incremento che deve avere il vettore rotante da uno step ad un altro ad ogni colpo di clock. E' quindi possibile esprimere la frequenza del segnale di uscita come:

$$f_{OUT} = (M \times f_{melk})/2^n$$

Ovviamente più grande è il modulo M e più grande sarà la frequenza del segnale di uscita, ovvero

arrivo in un minor tempo dal valore 0 al massimo valore consentito nell'accumulatore di fase a *n* bit, prima che ci sia overflow. D'altro lato però, peggiore sarà la qualità del segnale di uscita perché preleverò dalla look up table, secondo blocco del sistema, un minor numero di valori di ampiezza da convertire successivamente mediante il DAC nel segnale analogico sinusoidale. Per aumentare la massima frequenza di uscita si può aumentare la frequenza del master clock di riferimento. Per il teorema di Nyquist la massima frequenza del segnale di uscita è pari alla metà della frequenza di clock, ma questo è un limite teorico. Per avere una buona qualità del segnale di uscita, cioè un buon numero di campioni, la frequenza in uscita deve rimanere a valori circa 5-10 volte inferiori alla frequenza di riferimento utilizzata dall'AD9833.

Come anticipato, il secondo blocco del sistema, è la tabella di conversione fase/ampiezza che non è altro che una memoria nella quale sono memorizzati i valori in ampiezza della funzione sinusoidale. Il dato digitale prelevato dall'accumulatore di fase viene troncato prelevando i bit significativi e passato in ingresso alla tabella di conversione, all'uscita della quale mi ritroverò il valore dell'ampiezza che, anch'esso troncato, verrà passato al DAC per la conversione digitale/analogica.

E' presente inoltre il blocco del registro di fase, all'interno del quale viene memorizzato il valore di partenza del conteggio in modo da poter variare la fase del segnale in uscita.

Possiamo calcolare la minima risoluzione teorica consentita da un dispositivo con frequenza di clock di 25MHz e un accumulatore di fase a 28bit (non considerando il troncamento che avviene nel passaggio dall'accumulatore di fase alla look up table). Ponendo il passo M=1 risulta f<sub>OUT</sub>=0,09Hz.

Se lo stesso dispositivo è collegato ad una frequenza di clock di 4MHz la  $f_{OUT}$  sarà uguale a 0,014Hz. Si noti che la risoluzione aumenta ma la massima frequenza in uscita è diminuita.

Ovviamente il sistema non è esente da problemi tipici dei sistemi digitali e che dipendono da vari fattori ed in particolare dal *jitter* (variazione dei valori nominali dell'oscillatore) presente sul segnale di clock, dall'errore di troncamento fra l'accumulatore di fase e la look up table e dall'errore di quantizzazione del DAC.

La bontà di un sintetizzatore DDS rispetto ad un altro è misurata mediante l'SFDR (Spurious Free Dynamic Range) definito come il rapporto tra l'ampiezza della componente a frequenza  $f_o$  (frequenza principale) e l'ampiezza più grande delle componenti spurie presenti nello spettro. Si misura in decibel e più è grande questo valore, migliore è il comportamento del componente.

L'SFDR dipende dalla frequenza di uscita rispetto a quella di clock, infatti si ha un SFDR migliore per quelle frequenze particolari per le quali i troncamenti hanno meno effetto sull'errore.

Il segnale in uscita presenta inoltre delle armoniche a frequenze multiple rispetto a quella di clock e uscita, le quali possono essere attenuate mediante dei filtri in uscita.

Molto critico è il dimensionamento del circuito di amplificazione in uscita, così come la disposizione dei componenti e delle piste, in quanto con questi chip si raggiungono alte frequenze.

#### L'integrato AD9833

L'integrato AD9833 prodotto dall'Analog Device è un dispositivo che è in grado di generare una forma d'onda sinusoidale, triangolare o quadra, ad una frequenza che oscilla da 0 a 12,5MHz con clock di riferimento massimo di 25MHz (sono presenti sintetizzatori DDS anche con frequenze superiori, prodotti dalla stessa Analog Devices). Il dispositivo si alimenta con una tensione continua da 2,3V a 5,5V e assorbe solamente 12,5mW con tensione di alimentazione 3V, pertanto è adatto per sistemi alimentati a batteria e comunque portatili, date anche le minuscole dimensioni (package MSOP 10 pin).

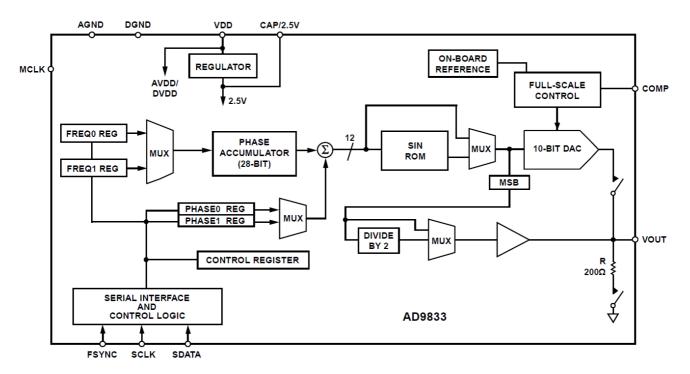

L'integrato è programmabile attraverso un bus tipo SPI a tre fili, in grado di operare a frequenze di 40MHz. In Figura 4 è mostrato lo schema a blocchi dell'AD9833.

Figura 4: Schema a blocchi AD9833.

E' possibile riconoscere i seguenti blocchi principali, NCO (Numerically Controlled Oscillator), modulatore di frequenza e di fase, una SIN ROM, un DAC e un regolatore lineare.

In particolare l'NCO si compone di due registri di frequenza, un accumulatore di fase a 28bit, due registri di fase collegati ad un sommatore.

L'accumulatore di fase divide l'intervallo da 0 a  $2\pi$  in un numero di passi discreti pari a  $2^{28}=268\cdot435\cdot456$

L'accumulatore di fase ha in ingresso il valore (la tuning word) prelevato da uno dei due registri di frequenza a 28bit (FREQ0 e FREQ1), singolarmente selezionabili mediante l'impostazione del bit FSELECT che ci consente inoltre di passare senza discontinuità da un valore di frequenza ad un altro. In uscita all'accumulatore può essere aggiunto uno sfasamento memorizzato in due registri (PHASE0 e PHASE1) singolarmente selezionabili mediante l'impostazione del bit PSELECT.

Il valore numerico in uscita dall'accumulatore di fase viene convertito in ampiezza mediate la SIN ROM. Il valore a 28bit viene troncato a 12bit (2<sup>12</sup>=4<sup>.</sup>096 valori). La SIN ROM può essere abilitata/disabilitata agendo sul bit D1 (mode).

Il valore di ampiezza proveniente dalla SIN ROM viene convertito in un valore analogico mediante un DAC a 10bit con tensione uscita di circa 0.6Vpp. Non è necessaria la resistenza di carico in uscita in quanto all'interno del dispositivo ne è presente una da  $200\Omega$ .

Infine, il regolatore interno, provvede a fornire alimentazione alla sezione digitale del dispositivo che

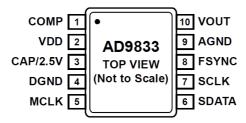

funziona a 2,5V, abbassandone la tensione di alimentazione. Se la tensione di alimentazione è minore o uguale a 2,5V, il regolatore può essere bypassato collegando insieme i pin  $V_{dd}$  e CAP. Il dispositivo è fornito in package MSOP a 10 pin (Figura 5).

Figura 5: Pinout dell'integrato AD9833.

In particolare nella Tabella 1 si riporta la descrizione di ogni pin.

| PIN N. | NOME     | DESCRIZIONE                                                                                                                                                                                                                |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | COMP     | Questo pin è utilizzato per disaccoppiare il DAC.                                                                                                                                                                          |

| 2      | VDD      | Pin di alimentazione compresa tra 2,3V a 5,5V. E' necessario collegare due condensatori di disaccoppiamento rispettivamente da 0.1uF e 10uF fra il pin VDD e AGND.                                                         |

| 3      | CAP/2,5V | Questo pin serve per collegare una capacità di disaccoppiamento da 100nF dedicata alla parte digitale del dispositivo alimentata a 2,5V mediante il regolatore interno. La capacità va collegata fra il pin stesso e DGND. |

| 4      | DGND     | Massa dei circuiti digitali.                                                                                                                                                                                               |

| 5      | MCLK     | Clock di riferimento per la parte DDS.                                                                                                                                                                                     |

| 6      | SDATA    | Su questo pin va collegato il dato seriale di ingresso a 16 bit.                                                                                                                                                           |

| 7      | SCLK     | Clock del sistema bus di comunicazione. Il dato è caricato ad ogni fronte di discesa del segnale.                                                                                                                          |

| 8      | FSYNC    | Quando il segnale applicato su questo pin va a zero il dispositivo avvia la ricezione dei dati.                                                                                                                            |

| 9      | AGND     | Massa della parte analogica.                                                                                                                                                                                               |

| 10     | VOUT     | Segnale in uscita.                                                                                                                                                                                                         |

**Tabella 1:** Descrizione dei pin dell' integrato AD9833.

## I registri di controllo dell'integrato AD9833

L'integrato AD9833 comunica con l'esterno mediante un bus SPI a tre fili. La linea SDATA, per il dato a 16bit da scrivere all'interno dei registri, la linea SCLK che è il segnale di clock del bus di comunicazione e che funziona sul fronte di discesa e infine la linea FSYNC che è il segnale di avvio della ricezione da parte del dispositivo.

Per ulteriori dettagli su questo protocollo di comunicazione si faccia riferimento alla Brief Note L'interfaccia SPI sul sito www.laurtec.it.

L'integrato dispone di un registro di controllo a 16bit, in Tabella 2 è riportato il significato di ogni bit.

| BIT | NOME     | FUNZIONE                                                                                                                                                                                                          |  |  |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| D15 | //       | Questo bit, in associazione con D14, consente di determinare in quale registro di frequenza, FREQ0 o FREQ1, caricare il valore.                                                                                   |  |  |  |  |

| D14 | //       | Questo bit, in associazione con D15, consente di determinare in quale registro di frequenza, FREQ0 o FREQ1, caricare il valore.                                                                                   |  |  |  |  |

| D13 | B28      | Quando questo bit è 1 il dispositivo è pronto a ricevere mediante due scritture consecutive, prima i 14 bit meno significativi e poi i 14 bit più significativi, il valore da caricare nei registri di frequenza. |  |  |  |  |

| D12 | HLB      | Questo bit serve per agire esclusivamente sui 14bit più/meno significativi senza alterare i rimanenti per effettuare operazioni di tuning.                                                                        |  |  |  |  |

| D11 | FSELECT  | Questo bit serve per stabilire quale valore nel registro di frequenza deve essere caricato nell'accumulatore di fase.                                                                                             |  |  |  |  |

| D10 | PSELECT  | Questo bit serve per stabilire quale valore nel registro di fase deve essere aggiunto all'accumulatore di fase.                                                                                                   |  |  |  |  |

| D9  | Reserved | Bit da settare a 0.                                                                                                                                                                                               |  |  |  |  |

| D8  | RESET    | Quando il bit è a 1 vengono resettati i registri interni.                                                                                                                                                         |  |  |  |  |

| D7  | SLEEP1   | Quando SLEEP1=1 il clock interno viene disabilitato e in uscita mi ritrovo l'ultimo valore caricato.                                                                                                              |  |  |  |  |

| D6  | SLEEP12  | Quando SLEEP12=1 spengo il DAC.                                                                                                                                                                                   |  |  |  |  |

| D5  | OPBITEN  | Con questo bit in associazione al bit D1(MODE) posso controllare il tipo di uscita, sinusoidale, triangolare, quadra.                                                                                             |  |  |  |  |

| D4  | Reserved | Bit da settare a 0.                                                                                                                                                                                               |  |  |  |  |

| D3  | DIV2     | Con questo bit in associazione a D5(OPBITEN) posso settare se deve essere passata in uscita il valore di frequenza MSB o MSB/2 .                                                                                  |  |  |  |  |

| D2  | Reserved | Bit da settare a 0.                                                                                                                                                                                               |  |  |  |  |

| D1  | MODE     | Con questo bit in associazione al bit D5(OPBITEN) posso controllare il tipo di uscita, sinusoidale, triangolare, quadra.                                                                                          |  |  |  |  |

| D0  | Reserved | Bit da settare a 0.                                                                                                                                                                                               |  |  |  |  |

Tabella 2: Descrizione dei bit di controllo dell'AD9833.

Maggiori dettagli sulle varie configurazioni e settaggio dei bit sono presenti nel datasheet del componente; in ogni caso si descrive nel dettaglio la scrittura di un valore di frequenza e di un valore di fase.

Per impostare il valore di frequenza in uscita si devono effettuare tre scritture da 16bit. Nella prima è necessario settare il bit B28=1 in modo che il dispositivo si prepari alla ricezione del valore di frequenza.

Nel secondo passaggio si scrivono i 14 bit meno significativi preceduti da i due bit D15 e D14 che servono per far capire al dispositivo se il valore va scritto del registro FREQ0 o FREQ1 e infine nel terzo passaggio i 14 bit più significativi, sempre preceduti da i bit D15 e D14 opportunamente selezionati. Per esempio se dobbiamo scrivere il valore nel registro FREQ0:

#### 1° scrittura

| 0   | 0   | 1   | X   | X   | X   | X  | X  | X  | X  | X  | X  | X  | X  | X  | X  |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

#### 2° scrittura

| 0   | 1   | LSB |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

#### 3° scrittura

| 0   | 1   | MSB |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Invece per scrivere un valore di fase (12 bit) basterà una sola scrittura settando D15 e D14 a 1, e a seconda del valore che assume il bit B28, il valore verrà caricato nel registro PHASE0 o PHASE1.

#### Libreria AD9833 per PIC18

La libreria descritta in questo articolo è stata sviluppata per PIC18 ed è testata su PIC18F4550 con quarzo a 20MHz. Le prove sono state fatte acquistando su ebay una schedina con già montato sopra l'integrato AD9833, un oscillatore a 25MHz e tutti i componenti di contorno; questo perché il package MSOP, a causa delle dimensioni, risulta difficile da saldare. La schedina, dotata di strip a 7 pin, è facilmente installabile sulla scheda di espansione di Freedom II, ovvero la scheda PJ7011.

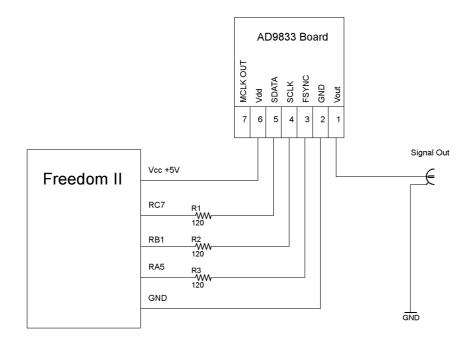

Per il collegamento dati vengono utilizzati i 3 pin standard per la comunicazione SPI, ovvero:

- RB1 per SCLK (SCK Signal Clock Master Mode)

- RC7 per SDATA (SDO Serial Data Output)

- RA5 per FSYNC (SS Slave Select)

Bisogna ricordarsi di settare i registri TRIS delle rispettive porte utilizzate come output. L'alimentazione della scheda AD9833 di 5Vdc è prelevata da Freedom II. Il segnale in uscita si preleva dal pin Vout della scheda AD9833.

Nel file header AD9833.h sono dichiarate diverse costanti ed i prototipi di funzioni. L'implementazione delle funzioni invece è riportata nel file sorgente AD9833.c che utilizza, per il proprio funzionamento, la libreria spi.h di Microchip; questa, funzionando a 8 bit, richiede la scomposizione dei dati ricevuti in ingresso che invece sono a 16bit. In pratica l'operazione di scrittura si divide nei seguenti passi:

- 1) Si porta FSYNC a 0.

- 2) Si scrivono gli 8 bit MSB.

- 3) Si scrivono gli 8 bit LSB.

- 4) Si porta FSYNC a 1.

La libreria implementa le seguenti funzioni:

```

void init AD9833 (unsigned char fmclk)

```

Con questa funzione si inizializza il dispositivo. Come parametro di ingresso si deve inserire il valore della frequenza dell'oscillatore di riferimento espressa in MHz.

```

void set frequency AD9833 (unsigned long freq value, unsigned char frequency register)

```

Con questa funzione si scrive il valore della frequenza in Hz in uscita (parametro freq\_value) e si decide in quale registro scrivere, REG0 registro FREQ0 e REG1 registro FREQ1

```

void tuning_frequency_AD9833(unsigned char tuning_step, unsigned char direction,

unsigned char frequency register)

```

Questa funzione serve per variare la frequenza del segnale di uscita in maniera fine. In ingresso di deve passare il valore espresso in bit, della variazione. Il passo più piccolo di 1bit corrisponderà alla minima risoluzione che dipende a sua volta dalla frequenza MCLK, per esempio 0,09Hz con oscillatore a 25MHz. Inoltre si può impostare la direzione della variazione, ovvero UP (incrementa) o DOWN

(decrementa) e in quale registro scrivere, REG0 registro FREQ0 e REG1 registro FREQ1.

```

void set_phase_AD9833 (unsigned short long phase_value, unsigned char phase_register)

```

Questa funzione permette d'impostare il valore della fase del segnale in uscita in decimi di grado, ovvero da 0 a 3600, (parametro phase\_value) scegliendo anche in quale registro scrivere, REG0 registro PHASE0 e REG1 registro PHASE1.

```

void set function AD9833 (unsigned char function type)

```

Con questa funzione è possibile configurare il dispositivo e attivare/disattivare le varie funzionalità dello stesso.

In particolare sono definite le seguenti costanti da passare come parametro:

- 1 SIN Forma d'onda sinusoidale in uscita.

- 2 TRIANGLE Forma d'onda triangolare in uscita.

- 3 SQUARE Forma d'onda quadra in uscita.

- 4 FREQUENCYO OUT Si utilizza il registro FREQ0 in ingresso all'accumulatore di fase.

- 5 FREQUENCY1 OUT- Si utilizza il registro FREQ1 in ingresso all'accumulatore di fase.

- 6 PHASE0 OUT Si aggiunge il valore del registro PHASE0 all'accumulatore di fase.

- 7 PHASE1\_OUT Si aggiunge il valore del registro PHASE1 all'accumulatore di fase.

- 9 SLEEP MODE Si spegne il DAC.

- 10 POWER ON Riaccendo il dispositivo dopo lo SLEEP mode

## Applicazione I: Generatore di funzioni

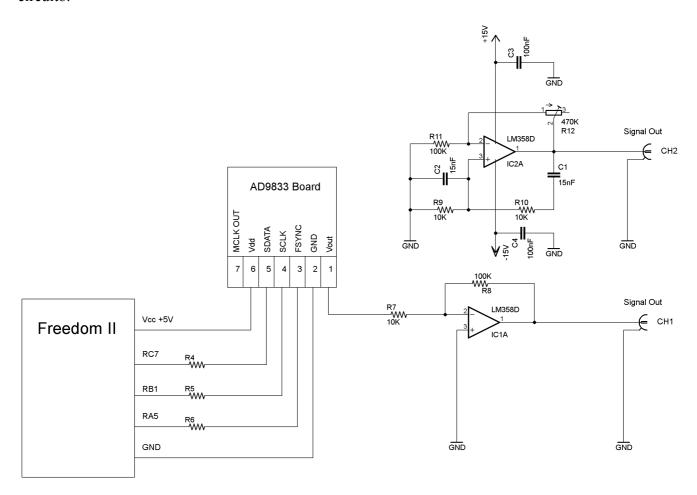

Per testare il sistema si è fatto uso della scheda Freedom II con a bordo il PIC18F4550 e si è montato la scheda contenente l'integrato AD9833 sulla scheda di espansione PJ7011. Lo schema elettrico è riportato in Figura 6, mentre il montaggio del sistema è riportato in Figura 7.

**Figura 6:** Schema elettrico di un semplice generatore d'onda.

Si noti la presenza delle resistenze R1, R2, R3. Queste sono state poste su ogni linea al fine di limitare problemi di picchi di tensione derivanti dal fatto che la comunicazione avviene su una linea di circa 10cm. Le resistenze permettono infatti di "rallentare" il segnale limitando il dV/dt, il che limita anche le radiazioni emesse dal bus stesso (dI/dt).

Figura 7: Realizzazione pratica del generatore di segnali.

In ultimo, si fa notare che le linee SPI sono in parte in comune con il modulo UART per cui, al fine di evitare problemi con quest'ultimo è bene rimuovere l'integrato MAX232 dalla scheda Freedom II.

Il programma di esempio utilizza il display LCD alfanumerico per visualizzare il valore di frequenza in uscita, la fase, il tipo di forma d'onda e il tipo di incremento/decremento della frequenza in uscita fra i seguenti valori, 1Hz, 10Hz, 10Hz, 10Hz, 10KHz, 50KHz, sintonia fine (FI). Il controllo di ogni funzione è implementata per mezzo dell'utilizzo dei tasti presenti sulla scheda Freedom II. In particolare la funzione di ogni tasto è riportata in Tabella 3.

| TASTO       | FUNZIONE                                                                                               |

|-------------|--------------------------------------------------------------------------------------------------------|

| BT1         | Aumenta la frequenza del segnale di uscita.                                                            |

| BT2         | Diminuisce la frequenza del segnale di uscita.                                                         |

| BT3         | Seleziona il tipo di forma d'onda in uscita (sinusoidale, triangolare, quadra).                        |

| BT4 + BT1   | Aumenta la fase del segnale di uscita (incremento fisso 10°).                                          |

| BTN4 + BTN2 | Diminuisce la fase del segnale di uscita (incremento fisso 10°).                                       |

| BTN4 + BTN3 | Selezione dell'incremento/decremento di frequenza (1Hz, 10Hz, 10Hz, 10Hz, 10kHz, 50kHz, sintonia fine) |

Tabella 3: Descrizione delle funzioni dei tasti.

Il sistema potrebbe essere facilmente implementato anche facendo uso di schede come Freedom Light o EasyUSB oltre che naturalmente su una millefori.

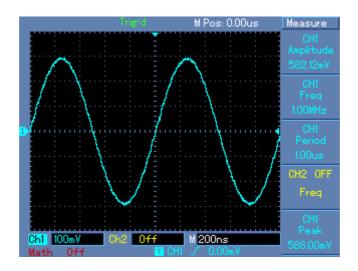

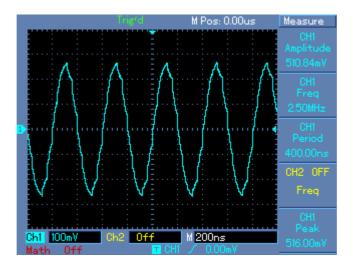

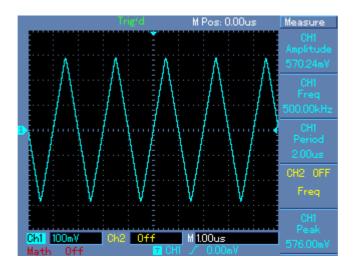

Attivando il sistema e collegando l'oscilloscopio all'uscita dell'AD9833 è possibile vedere le varie forme d'onda. In Figura 8 si è riportato il caso si onda sinusoidale alla frequenza di 1MHz mentre in Figura 9 è riportato il caso a 2.5MHz.

Figura 8: Onda sinusoidale ad 1MHz.

Figura 9: Onda sinusoidale a 2.5MHz.

Si noti come in questo secondo caso, il segnale di uscita risulti maggiormente distorto, visto che ci si trova a frequenze circa 10 volte inferiori a quella del clock principale di 25MHz.

In ultimo è riportato il caso di un'onda triangolare.

Figura 10: Connessioni integrato AD9833.

In questo caso, avendo impostato il sistema per generare una frequenza di 500KHz si ha un segnale piuttosto "pulito". Anche se non riportata si ricorda che l'AD9833 permette di generare anche un'onda quadra, la quale viene creata non dalla derivata dell'onda triangolare ma semplicemente visualizzando il bit più significativo del valore convertito dal DAC.

Si osservi che l'ampiezza del segnale è piuttosto ridotta (Vout =  $\sim$ 0.6Vpp) per cui per applicazioni pratiche è bene provvedere ad amplificare il segnale.

### Applicazione II: Figure di Lissajou

In questo secondo esempio si fa uso di un piccolo circuito esterno (oscillatore secondario) per mezzo del quale, facendo uso di un oscilloscopio in modalità XY è possibile visualizzare le figure di Lissajous (<a href="http://it.wikipedia.org/wiki/Figura\_di\_Lissajous">http://it.wikipedia.org/wiki/Figura\_di\_Lissajous</a>). In Figura 11 è mostrato lo schema del circuito.

Figura 11: Schema del circuito di prova.

L'amplificatore operazionale LM358 è alimentato con una tensione duale di 15Vdc. Il primo opamp, in configurazione di amplificatore invertente con guadagno in modulo pari a 10, serve per amplificare il debole segnale in uscita dall'AD9833 che raggiunge in questo modo circa 6Vpp. Tale segnale deve essere collegato al canale CH1 dell'oscilloscopio.

Il secondo opamp è stato configurato come oscillatore a ponte di Wien. I componenti sono stati scelti in modo da avere una frequenza di oscillazione di 1000Hz. Si è scelta una frequenza bassa perché il circuito è montato su breadboard (Figura 7). L'uscita dell'oscillatore di Wien deve essere collegata al canale CH2 dell'oscilloscopio.

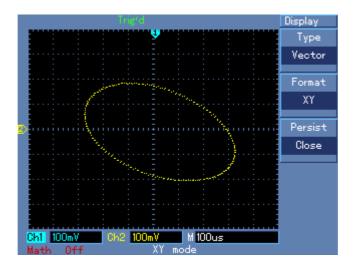

Alimentando la scheda Freedom II si visualizzeranno sull'oscilloscopio le due forme d'onda, quella in uscita dall'AD9833 e quella generata dall'oscillatore. "Agganciando" il trigger su di un canale si vedrà l'altra forma d'onda scorrere sullo schermo. Agendo sui tasti è possibile variare la frequenza in uscita all'AD9833 fino a rendere i due segnali isofrequenziali (con l'oscillatore a 25MHz montato sulla scheda AD9833 non si riesce bene a farlo per cui si può sostituire l'oscillatore con uno da 8MHz per avere una precisione migliore). A questo punto si può variare la fase del segnale e portando l'oscilloscopio in modalità XY si possono visualizzare le figure di Lissajous .

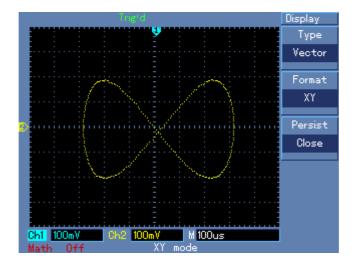

In Figura 12 e Figura 13 sono riportati due esempi ottenuti per mezzo dell'AD9833 abbinato ad un generatore di funzioni impostato a 2KHz e 1KHz. La differenza di fase viene a dipendere rispettivamente dall'inclinazione del cerchio e dalla forma dell'8.

La Figura 12 mostra che CH1 (AD9833) e CH2 (Generatore di funzione) hanno la stessa frequenza ma uno sfasamento di circa 45°.

Figura 12: CH1 2000Hz - CH2 2000Hz (sfasamento 45°).

**Figura 13:** *CH1* 1000Hz – *CH2* 2000Hz (sfasamento 0°).

In Figura 13 si può notare che CH1 ha una frequenza la metà di CH2 ma sono circa in fase (o con sfasamento 90° - 180°).

#### **Conclusioni**

Gli esempi mostrano come sia semplice l'utilizzo della libreria, che grazie a poche funzioni permette il controllo dell'integrato. Gli esempi presentati seppur esplicativi dell'utilizzo della libreria, non presentano da un punto di vista hardware, un sistema completo. Aggiungendo hardware opportuno attorno all'integrato AD9833 è possibile realizzare generatori di funzione professionali. Ciononostante l'utilizzo di un display alfanumerico già permette di vedere come sia possibile avere una semplice interfaccia per uno strumento professionale.

#### **Bibliografia**

- [1] www.LaurTec.it: Sito dove poter scaricare aggiornamenti dell'articolo e "RS232 Terminal".

- [2] www.microchip.com: Sito dove scaricare i datasheet del PIC16F88 e MPLAB-X.

- [3] www.analog.com: Sito dell' Analog Semiconductor.

- [4] Analog Device Datasheet AD9833

- [5] Analog Device AN1070 "Programming the AD9833/AD9834"

- [6] Analog Device MT085 "Fundamentals of Direct Digital Synthesis (DDS)"

- [7] Analog Device AN837 "DDS-Based Clock Jitter Performance vs. DAC Reconstruction Filter Performance"

- [8] Analog Device "A Technical Tutorial on Digital Signal Synthesis"

- [9] Analog Dialogue 38-08, August (2004) "All About Direct Digital Synthesis"

# **Indice Alfabetico**

| A                                 |         | Nyquist                     | 7      |

|-----------------------------------|---------|-----------------------------|--------|

| accumulatore di fase              | 6       | P                           |        |

| AD9833                            | 8       | phase_value                 | 13     |

| Analog Device                     | 8       | PHASE0                      |        |

| C                                 |         | PHASE0 OUT                  | 13     |

| contatore binario                 | 6       |                             |        |

| conversione fase-ampiezza         | 6       | PHASE1 OUT                  | 13     |

| D                                 |         | PIC18F4550                  | 14     |

| D14                               | 11      | PJ7011                      | 14     |

| D15                               | 11      | ponte di Wien               | 17     |

| DAC                               | 5, 7    | POWER_ON                    | 13     |

| DDS                               | 5       | PSELECT                     |        |

| Digital Analog Converter          | 5       | $\mathbf{S}$                |        |

| Direct Digital Synthesis          | 5       | SCK                         | 12     |

| display LCD                       | 15      | SCLK                        | 10, 12 |

| DOWN                              | 12      | SDATA                       | 10, 12 |

| F                                 |         | SDO                         | 12     |

| figure di Lissajous               | 17      | Serial Data Output          | 12     |

| Freedom II                        | 14      | SFDR                        | 7      |

| FREQ0                             | 8, 11   | Signal Clock Master Mode    | 12     |

| FREQ1                             | 8, 11   | SIN                         | 13     |

| FREQUENCY0_OUT                    | 13      | SIN ROM                     | 8      |

| FREQUENCY1_OUT                    | 13      | sintetizzatori DDS          | 8      |

| FSELECT                           | 8       | Slave Select                | 12     |

| FSYNC                             | .10, 12 | SLEEP_MODE                  | 13     |

| J                                 |         | SPI                         | 8      |

| jitter                            | 7       | spi.h                       | 12     |

| L                                 |         | Spurious Free Dynamic Range | 7      |

| Lissajous                         | 17      | SQUARE                      | 13     |

| LM358                             | 17      | SS                          | 12     |

| look up table                     | 6       | T                           |        |

| M                                 |         | teorema di Nyquist          | 7      |

| MCLK                              | 12      | Tester per linee            | 4      |

| modulatore di frequenza           | 8       | TRIANGLE                    | 13     |

| Modulatore di segnale             | 4       | TRIS                        | 12     |

| modulo M                          | 6       | tuning word                 | 8      |

| MSOP                              | 8       | $\mathbf{U}$                |        |

| N                                 |         | UP                          | 12     |

| NCO                               | 8       | $\mathbf{V}$                |        |

| Numerically Controlled Oscillator | 8       | vettore rotante             | 6      |

## History

| Data     | Versione | Autore        | Revisione      | Descrizione Cambiamento         |

|----------|----------|---------------|----------------|---------------------------------|

| 12.12.13 | 1.0a     | Dario Di Turi | Mauro Laurenti | Correzione errori di battitura. |

| 22.01.13 | 1.0      | Dario Di Turi | Mauro Laurenti | Versione Originale.             |